왜 한국은 대만에 추월당할까? (3)

페이지 정보

조회 3,896회 작성일 23-04-24 17:25

본문

왜 한국은 대만에 추월당할까? (3)

우리나라 반도체 정책을 보면 왜 한국이 대만에 추월을 당하는지 묻는 것이 의미 없다는 생각을 하게된다. 2000년에 이미 대만의 시스템 반도체 정책 부분은 한국과 한참 다르게 운용하고 그간 23년간의 운용과 성과가 대만과의 차이를 만든 것이다.

시스템반도체 부분은 30년 전에는 대만보다 우리가 앞서거나 수준이 비슷했다. 요즘 잘 나가는 미디어텍은 지금은 없어진 토마토LSI, 엠텍비젼, 코어로직에 보다 작은 회사였다.

TSMC 는 1987년 2월 21일 세워졌다. 그무렵 우리나라에서도 컴퓨터 메인보드 등을 만드는 회사가 있었고 우리가 메모리에 집중하는 사이 대만은 VIA 등에서 인텔 CPU 와 마이크로 코드가 비슷한 CPU 를 만들었다. 이것이 1995년 경 이었다. 내 기억에 Cyrix 같은 회사에서 CPU를 만든었던 기억이 있고 아마도 이것이 AMD와 엔비디아 같은 회사가 되는 토양이 되었을 것이다. 우리나라 카이스트에서도 80386 같은 CPU를 만들고 있었다. 중간에 무슨이유인지 그만 두었지만.

팹리스 반도체 회사가 갑자기 뚝 떨어지지 않는다. 저런 회사의 공통점은 연구개발 시제품 제조 단계에서 십 수년간 파운드리의 전폭적인 지원을 받는다는 점이다.

고려시대 고려청자를 생각해 보면 도공이 영롱한 비취색을 얻기위해 평생을 거쳐 유약 재료와 점토 선정, 화력을 바꿔가며 트라이엔 에러 테스트 하고 마침내 그 노하우를 만들어 내는 이야기가 있다. 생각해 보면 도공이 그런 시제품 테스트를 하기 위한 그 비용은 도공이 시장에서 벌어 왔을까? 당시 권문세가나 귀족같은 누군가의 후원이나 도와주는 것이 없으면 불가능한 일이다.

메모리 반도체만 해도 오늘날의 메모리 반도체를 보유하기 위해서 국가적 도움과 지금도 이어지는 세제나 전력, 인프라, 시설투자, 금융, 수출, 해외정책 등의 도움은 엄청난 것이다.

팹리스의 가장 큰 고충은 시제품 제작과 테스트이다. 팹리스의 R&D 비용 구조는 비싼 고급 연구인력은 기본이고 IP, FPGA. RTL, 프론트엔드, 백엔드, 마스크, 페키지, 테스트, PCB, 인증 비용으로 구분된다.

이 중에서 보틀 넥이 되는 부분이 IP, 프론트, 백엔드, 마스크 비용인데 대만 TSMC 는 IP, 프론트, 백엔드, 마스크, 부분을 정부 지원받아 무료 수준으로 연결해 줄것 같다.

반면에 우리나라는 시제품 만드는 비용이 엄청난데 이 비용 구조에서 팹리스가 망가지게 된다. 답답한 것은 연구개발 단계에서 시제품 개발은 최소한 5번은 하게 된다. 생각해 봐라. 고려청자를 만들때 한번에 도공의 퀄을 통과 하는가? 일반인이 보기에는 아무런 문제가 없어도 도공은 애써 만든 도자기를 깨뜨려 버린다. 한 번에 절대 안된다. 결국 좋은 반도체를 만들기 위해서는 수십번 수백번의 테스트와 비용이 소요되는데 국내에서는 이런 비용이 너무 비싸게 소요된다.

그래서 레거시 공정이나 미세공정에서 국내 시생산을 못하니 TSMC 로 가게 되는 것이다. 국내 팹리스가 삼성, 동부, SK 파운드리를 외면 하고 해외 TSMC, GF, SMIC, UMC, HHNEC, Tower, XFab 같은 외부 파운드리를 기웃 거리는 것은 국내 파운드리 서비스 문제가 심각한 것이다.

우리나라 중소기업이나 학교 연구소가 해외 DSP를 사용하고 파운드리에 팹을 흘리는 것같이 대만이나 싱가폴 연구소가 한국 삼성이나 동부 매그나칩에 테스트 런을 흘리는가? 내가 알기로는 대만은 고사하고 해외 중소기업이나 연구소 학교가 한국 파운드리에 테스트 런을 흘렸다는 기록은 유사 이래 들어보지 못했다. 그만큼 한국의 파운드리와 DSP (Design Service Provider)의 경쟁력이 취약 하다는 뜻이다.

이런 상황에서 한국 팹리스나 한국 팹을 사용하고자 하면 IP, 디자인 서비스, 비용 등은 턱없이 비싸고 고 자세이다. 이게 심각한 것이 한국 팹리스가 DSP에 한번 견적을 받으면 다른 DSP 를 통해서는 같은 파운드리를 사용할 수 없도록 하는 이상한 정책도 있다. 파운드리가 3개 밖에 없고 DSP가 몇 개 안되니 파운드리를 등에 업고 호가호위 하는 것이다.

견적 한번 요청 했는데 파운드리를 사용할 때 DSP에 거래가 Lock이 된다는 뜻이다. 즉 A 회사는 B DSP 의 테렉토리 속칭 나와바리가 된다. 이렇게 되면 팹리스는 DSP가 던져 주는 조건과 가격대로 따라가야 한다. 견적을 주기 전에는 이런 저런 조건과 가격 혜택을 주겠다는 감언이설을 듣고 견적 한번 받았을 뿐인데 그 파운드리를 사용하려면 항상 그 DSP를 이용해야 한다는 별 희안한 정책을 파운드리가 고수하고 있다. 아마도 파운드리가 DSP의 로비를 받았을 수 도 있다.

사실 넓은 입장에서 보면 팹리스가 IP사, DSP, 파운드리, OSAT에 대해서 갑의 입장이다. 그런데 1995 ~ 2015 년까지 국내 팹리스는 물량이 많은 회사는제외하고 삼성전자에 테스트런을 흘릴 수 없었다. 웨이퍼 케파가 자사 물량도 빠듯한데 고객사 주문을 받을 수 없다는 것이다.

동부와 매그너칩은 180-110 나노 프로세스에 20년째 머물러 있다. 90-14나노 수준의 8, 12인치 공정은 만들어 볼 수 없다. 2000년 이전에는 삼성만 서비스 하는 미세공정 파운드리를 이용하는 것은 불가능했다.

파운드리 입장에서는 한국 팹리스 회사는 테스트만 하고 양산을 못 간다고 불평한다. 글세 파운드리가 제대로된 IP 가 없고 양산 경험이 부족해서 공정이 흔들린다. 설계를 해도 설계한대로 출력이 안나오는데 어떻게 양산이 되겠는가? 그리고 시생산 로그가 쌓여야 양산을 하는데 RF 같은 공정에서 수 년간 개발해 놓은 프로세스가 없어지기 일쑤인데 어떻게 믿고 양산을 하겠냐고.

내가 보기에 한국에서 반도체 인력 15만명 양성 하겠다는데 이 중간의 IP, 프론트엔드 백엔드를 담당하는 DSP, 파운드리의 안정이 안되면 시스템반도체 산업은 망하게 된다. 대만 TSMC 가 9,000개의 회사와 연구소에 제품과 코드를 검증했다고 한다. 사실 시제품 한번 만들 때마다 수억 에서 수천억의 비용이 들어가는 것이라 팹리스에서 파운드리에 9000개의 다자인 부분에서 코드를 테스트 해 보다는 말은 연인원으로 수천만명의 피땀흘린 노고가 들어갔다는 말이다.

반도체 시제품 테스트를 해볼 수 없으니 양산을 못 하는게 당연한 것 아닐까? 그런데 한국 정치, 정책, 협회, 단체는 재벌이 원하는 대로 단순히 건물, 장비, 용수 같은 하드웨어에 목숨을 거니 반도체 산업이 망하고 있는 것이다.

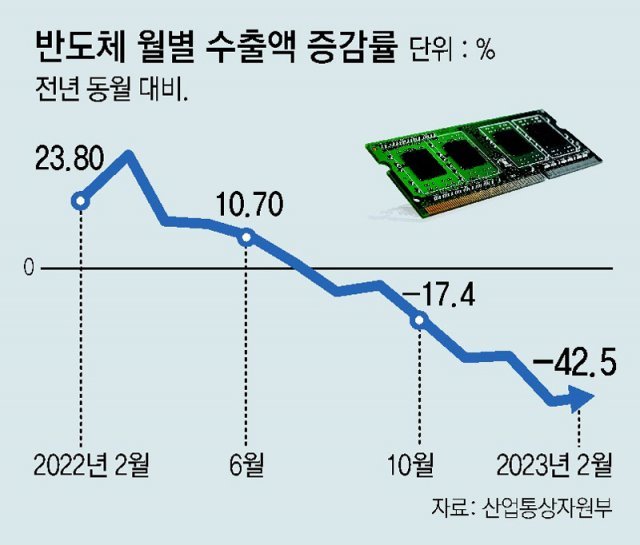

작년 대비 반도체 수출액이 45%가 감소 했다는데 이게 DRAM NAND 같은 시크리컬 산업이라 그런것이고 시스템반도체 산업도 경기를 타지만 메모리 수준은 아니다.

우리나라에서는 왜 TSMC같은 회사가 안나냐고? 그게 나오는게 이상한 거 아닌가?

추가로 그럼 엔비디아나 인텔은 왜 S전자에서 잘 만드냐고 반문을 하는 분들이 있을것 같다. 그런 회사는 규모가 크니 IP, 프론트, 백엔드 디자인을 다 그 회사에서 전담 한다. 즉 중간에 DSP가 많이 연관되지 않는다.

우리나라 팹리스가 왜 못 크냐고? 팹리스가 살아 남아 있는게 신기한 정책을 고수하고 있어서 아닐까? 저 중간의 문제를 정부가 돈으로 해결해야 한다. 반도체는 시제품 생산이 끝이 아니고 그게 본격적인 연구개발을 해도 된다는 의미라고. 이 분들이 말을 못알아 듣네.

아무도 말을 않하니 이런 이야기를 처음 듣겠네. 회사 운영자 중에 누가 이런 말을 정직하게 하겠음. 나같이 겁세포를 상실한 눈치없는 사람 빼고?

사랑과생각

#TSMC #Taiwan #Samsung #동부하이텍 #SoC #SystemonChip #Fabless #verilog #Design #DSP #foundry #chip #semiconductor #시제품 #MPC #NPC #MPW

관련링크

- 이전글왜 한국은 대만에 추월당할까 (4) 23.04.24

- 다음글왜 한국은 대만에 추월 당할까? (2) 23.04.24